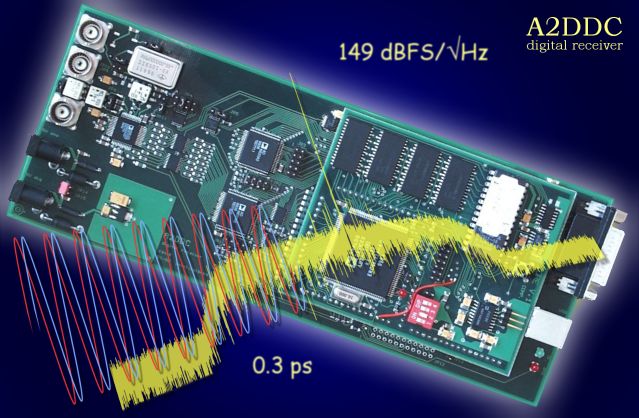

Dynamic range at fin 211 MHz : 143 dBFS/sqrt(Hz) @ fs 66 MHz

System jitter: <0.3 ps @ on-board 66 MHz clock

Intermodulation distortion: not measured yet

SFDR: not measured yet

Pictures of some measurements:

Frequency ResponseDynamic Range

Zero Input Noise Test (DC input just between words 0..0 and 1..1)

Test Bench - Matlab controled measurement(For GPIB and RS232 control are used CPORT and GPORT Minitoolboxes.)